![[FullCustomIC] MOSFET 기본 이론(1)_CMOS Schematic 등](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F9Tbsg%2FbtsFuM9xzsV%2FvLGGMWsWFk1PlnAayjlOxK%2Fimg.png)

■ Introduction

⦁ IC( Intergrated Circuit ) : 집적 회로, 다수의 Transistor가 하나의 칩에

⦁ VLSI( Very Large Scale Intergration ) : 초 고밀도 집접회로

★IC의 장점

1. Fast

2. Cheap → 고밀도 = 소형화 = 가격↓

3. Low Power

→ 엔지니어가 항상 고려해야하는 3가지

■ Si

SI : 4족(최외각 전자 4개) 원소로 공유 결합은 통해 stable한 상태가 됨 → 부도체 상태

때문에 도핑을 하여 반도체로 사용

- n-type dopant

: 5족 원소 사용 → 전자 다수

- p-type dopant

: 3족 원소 사용 → 정공 다수

=> n-type Mobility = p-type Mobility 2~3배

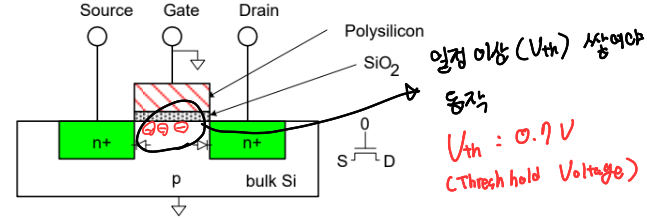

■ MOSFET

: MOSFET은 Transistor의 한 종류로 Metal-Oxide-Semiconductor Field Effect Transistor의 약자이다.

- Metal : 전극(Gate의 Polysilicon)

- Oxide : SiO2(부도체)

- Semiconductor : 도핑된 Source, Drain, Substrate(p라고 표기된 전체, p도핑된 si)

- Field Effect : 전계 효과를 이용

- 단자 구성(4개)

1. Source : 다수 캐리어를 내보내는 단자(pMOS : 정공, nMOS : 전자)

2. Drain : 다수 캐리어를 흡수하는 단자(pMOS : 정공, nMOS : 전자)

3. Gate : MOSFET을 작동(전류가 흐르도록)시킬 수 있는 단자

4. Body : Gate가 기능을 할 수 있게 하는 기준이 되는 단자

=> 전류 흐름 : nMOS Source → Drain, pMOS Drain → Source

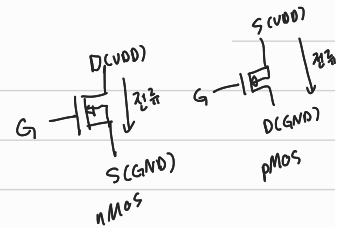

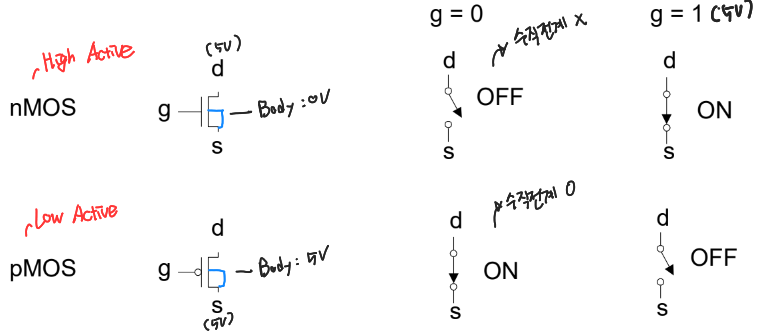

기호

nMOS

: Source와 Drain n도핑한 MOSFET, Substrate p도핑

@ nMOS) Gate 전압 > Body 전압

- 이유 : Gate 5V, Body 0V 전압 인가 → 수직 전계(Gate에서 Body 방향) 발생 → Gate에 정공 쌓이고,

Body에 n-channel(전자가 쌓이는 것) 발생 → Drain과 Source에 전위차가 생기면 전류 흐름

- 만약 Gate < Body 이면, Gate에 전자, Body에 p-channel 발생하여 npn Junction 생겨 전류 X

pMOS

: Source와 Drain p도핑한 MOSFET, Substrate n도핑

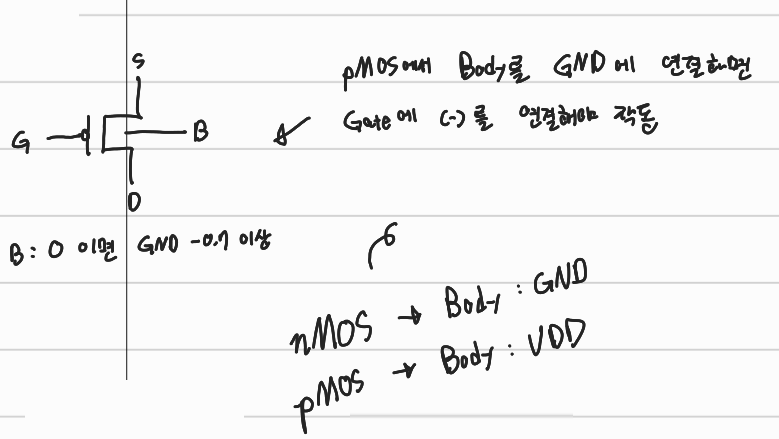

@ pMOS) Gate 전압 < Body 전압

- 이유 : Gate 0V, Body 5V 전압 인가 → 수직 전계(Body에서 Gate 방향) 발생 → Gate에 전자 쌓이고,

Body에 p-channel 발생 → Drain과 Source에 전위차가 생기면 전류 흐름

- 수평 전계는 바뀌어도 되지만 수직전계는 바뀌면 안됨

→ 수평 전계 바뀌면 전류 방향이 바뀌어 Source, Drain도 같은 방향으로 바뀜

(전류 방향 nMOS : Source → Drain, pMos : Drain → Source)

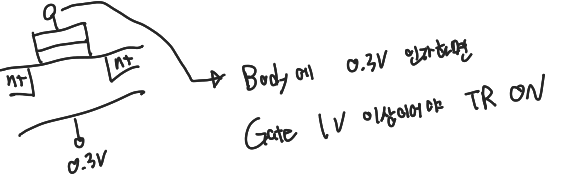

▶ 그럼 Gate와 Body 전위차가 얼마나 생겨야 작동?

=> Vth(Threshold Voltage, 문턱 전압), 일반적으로 0.7V

→ Vth 이상이면 MOSFET ON

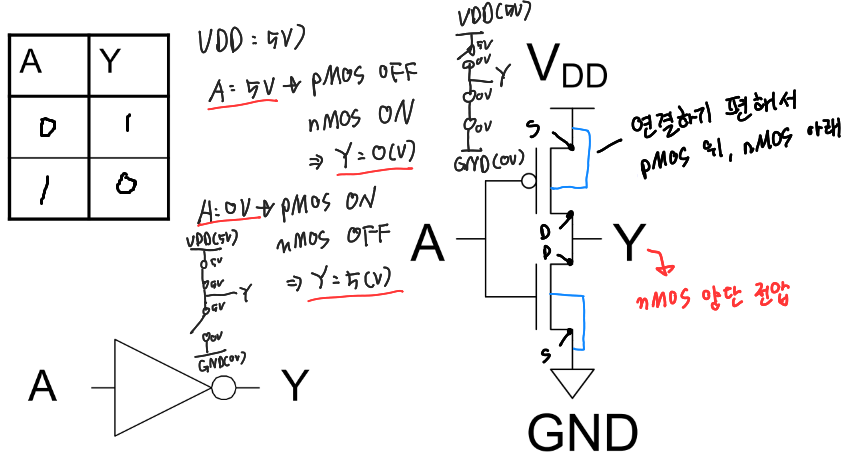

⦁ 일반적으로 Body를 Source에 연결하여 사용 → 3개의 단자(Source, Drain, Gate)만 사용하여 제어 가능

- nMOS Body = Source = GND

- pMOS Body = Source = VDD

⦁ 특별한 경우 아래와 같이 Gate 전압을 조절할 수 있음

⦁ MOSFET 스위치 동작을 잘 설명 해주는 그림

정리

| 구분 | pMOS | nMOS |

| Source, Drain dopant | p-type | n-type |

| channel | p-channel | n-channel |

| 전류 방향 | Source → Drain | Drain → Source |

| ON 조건 | Gate < Body | Gate > Body |

| Body 전압 | VDD(=Source) | GND(=Source) |

| Gate High 일 때 | OFF | ON |

| Mobility | 느림 | 빠름(2~3배) |

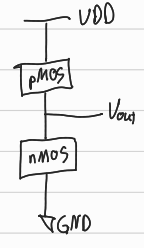

■ CMOS

: nMOS 와 pMOS로 이루어진 IC

Inverter

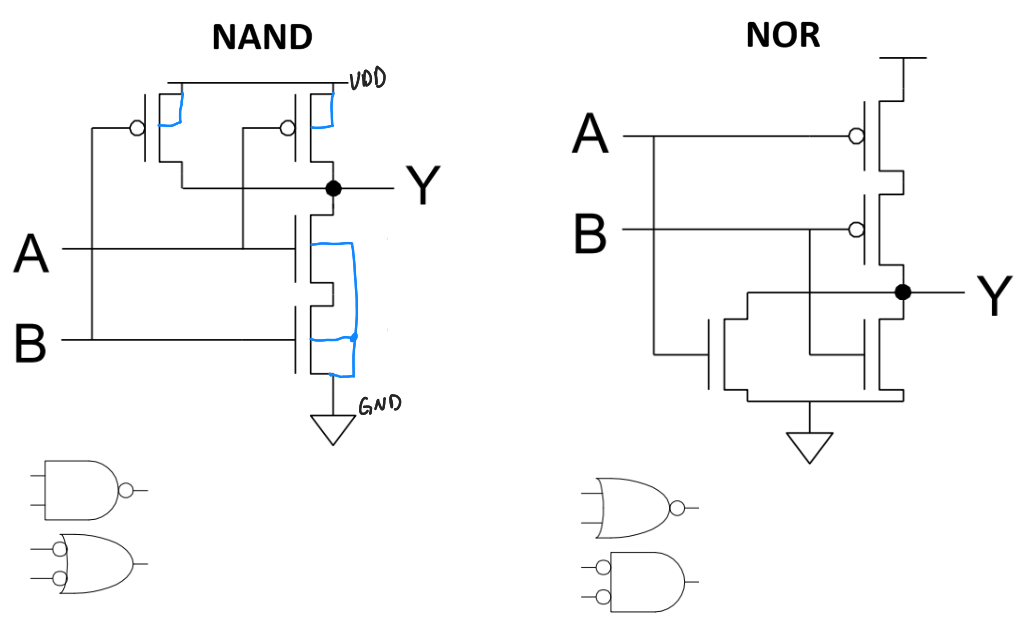

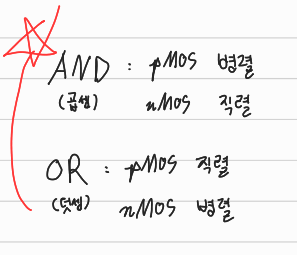

NAND, NOR

- NAND, NOR TR 개수 : 4개

- AND, OR TR 개수 : 4+2개(Inveter 2개 포함)

=> NAND, NOR 설계가 유리

CMOS Schematic

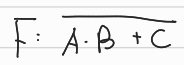

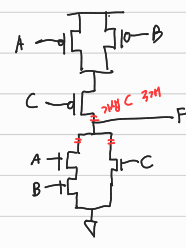

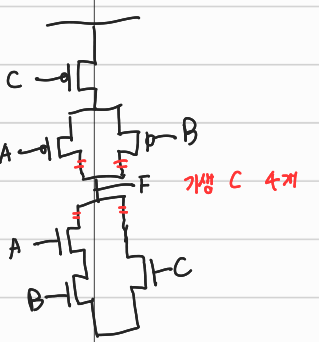

⦁ 예시)

→ 기생 C 적은 왼쪽이 더 유리

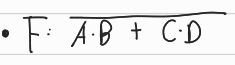

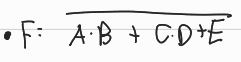

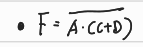

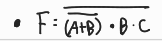

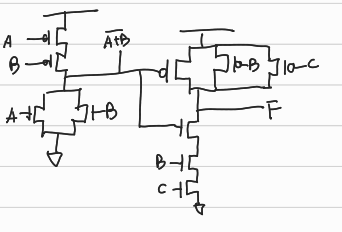

⦁ 문제 1)

⦁ 문제 2)

⦁ 문제 3)

⦁ 문제 4)

⦁ 문제 5)

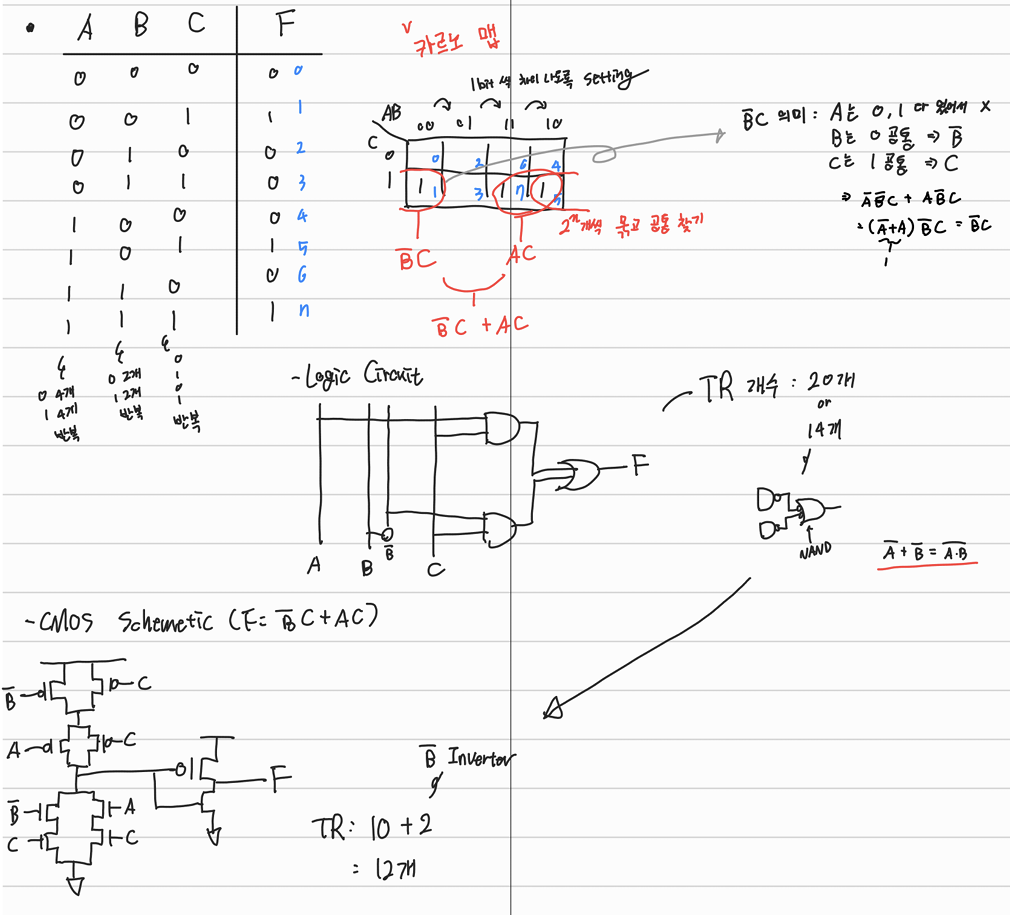

카르노 맵(Karnaugh Map)

→ CMOS Schematic 그리는 것이 TR을 가장 적게 사용할 수 있음(= Cost down)

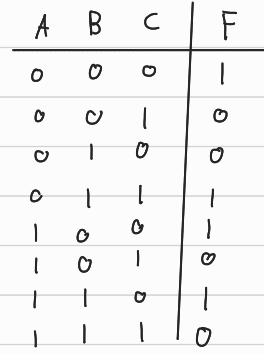

⦁ 문제 1. 아래 table에서 F의 식, Logic Diagram, CMOS Schematic은?

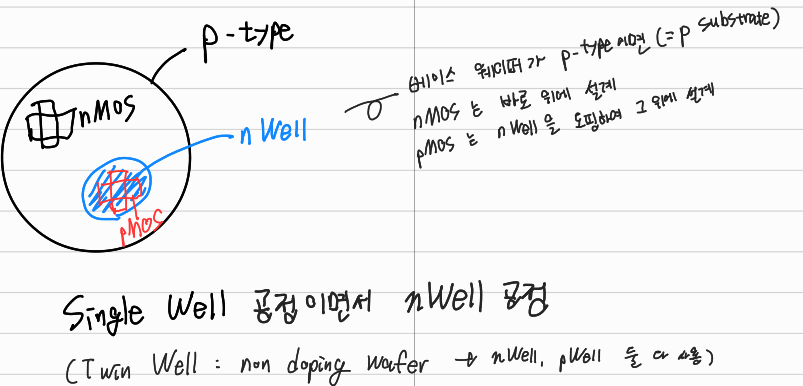

Single Well & Twin Well

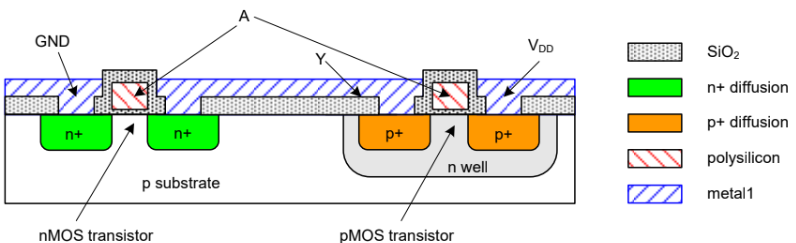

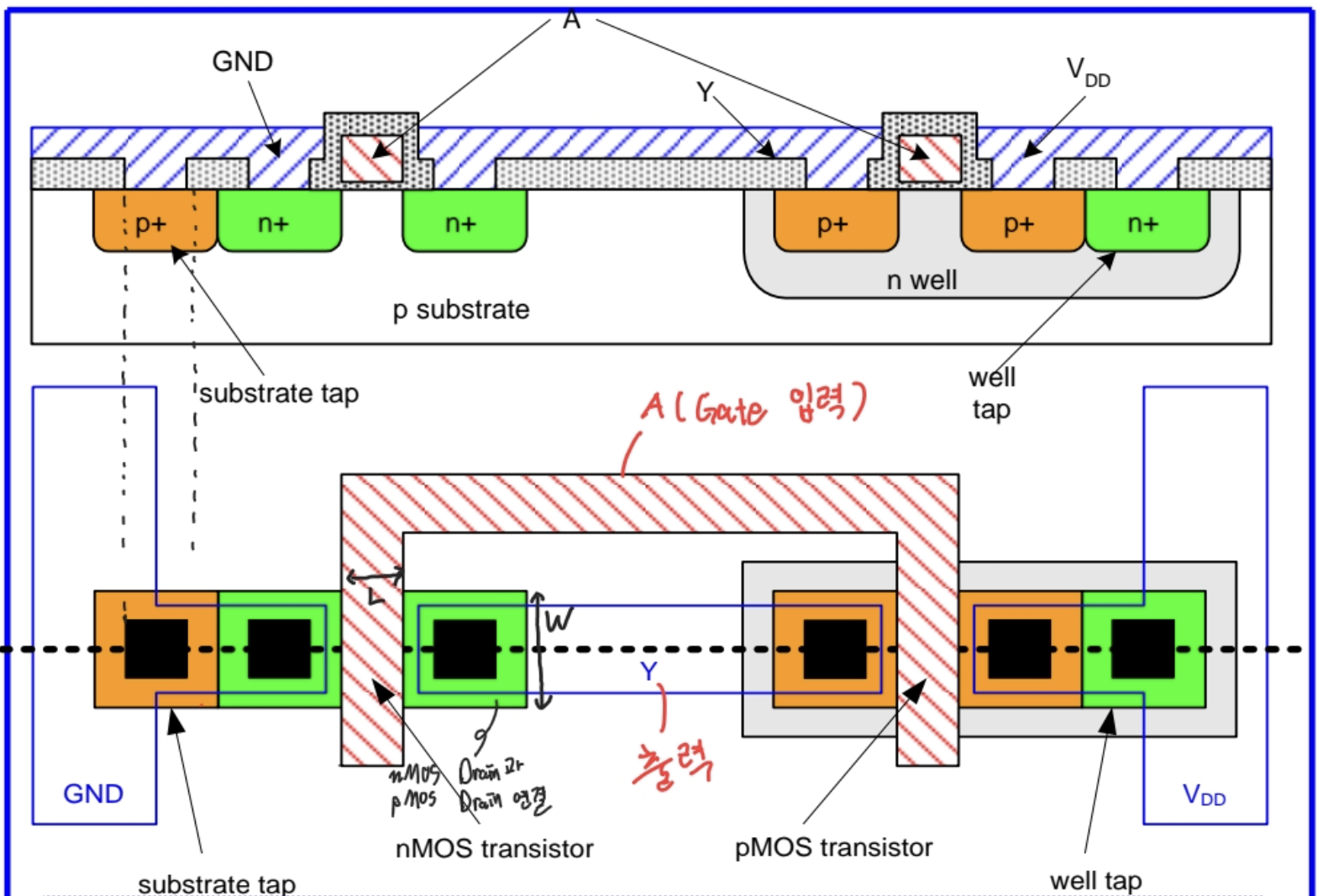

Cross-section

: 단면

⦁ 수직 단면

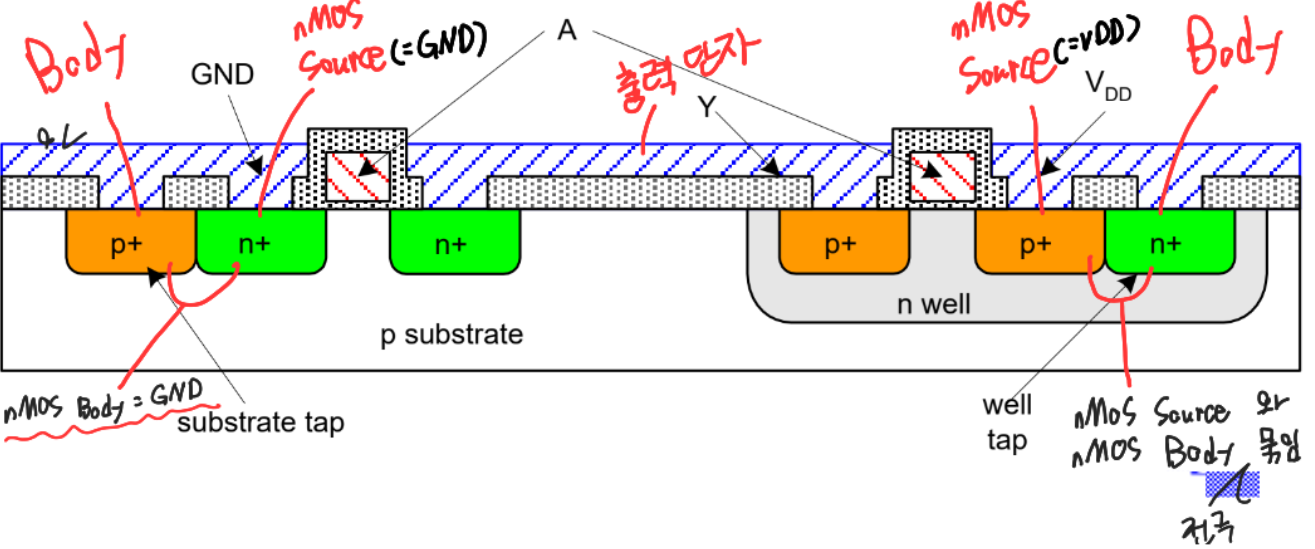

위 그림에서 잘못된 점 : Body 전극이 없음

↓ 해결

⦁ MOSFET에서 서술한 바와 같이

- pMOS(오른쪽)에서 Source와 Body 연결(=VDD)

- nMOS(왼쪽)에서 Source와 Body 연결(=GND)

⦁ Body = substrate 그 자체이기 때문에

- pMOS Body = n-dopant

- nMOS Body = p-dopant

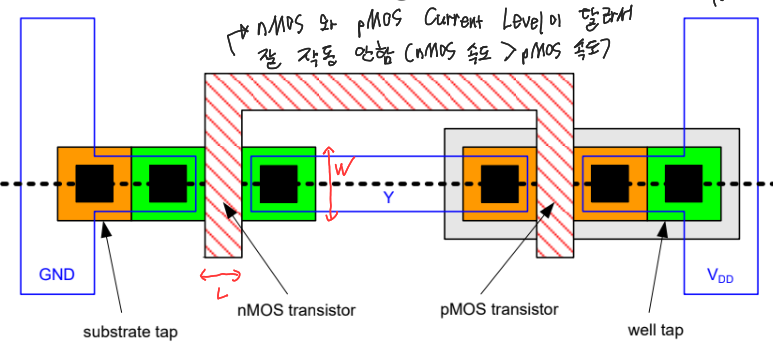

Mask-set

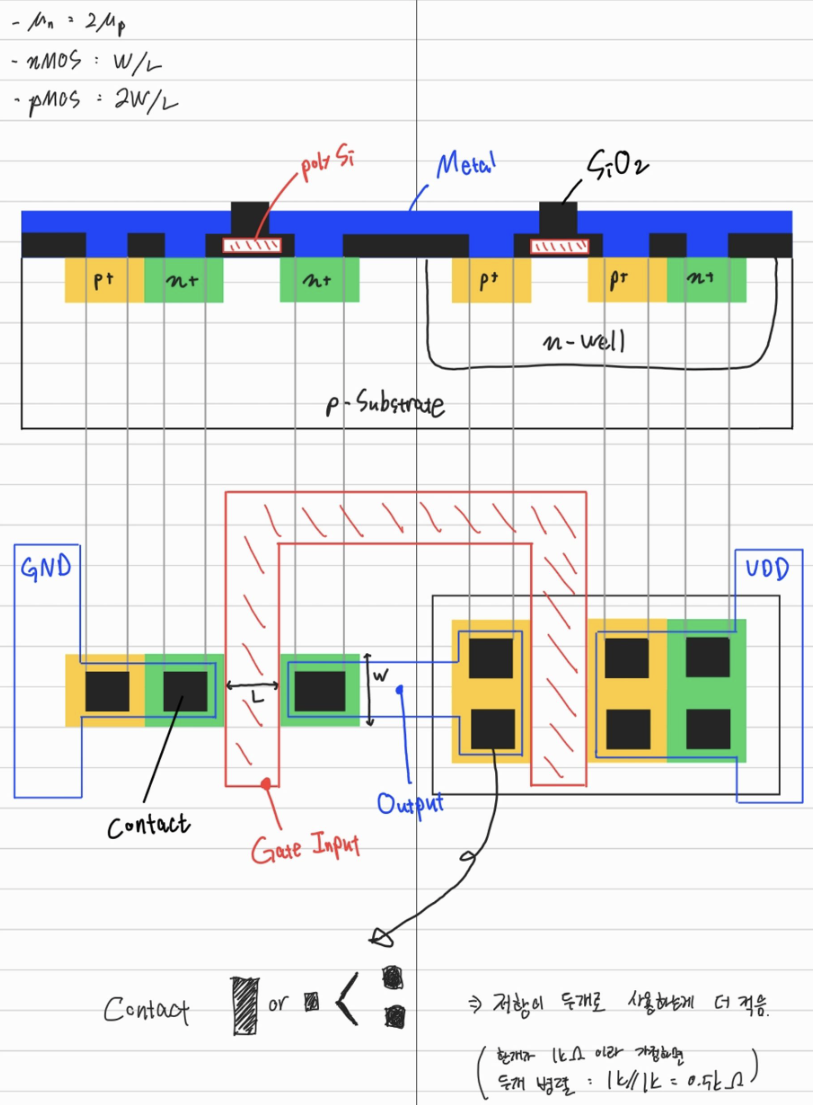

⦁ 수평 단면

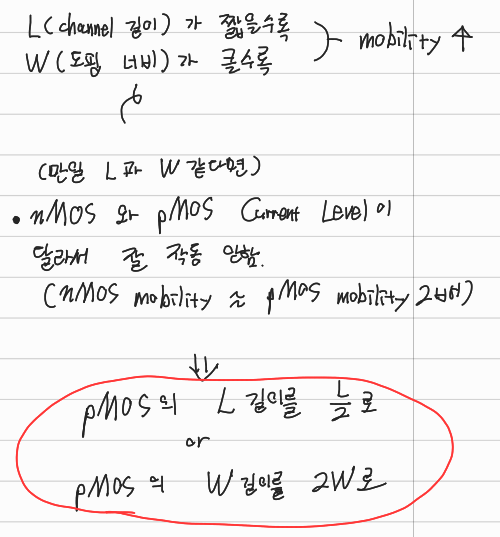

→ nMOS와 pMOS의 mobility를 맞추기 위해 L과 W 길이를 조절

- L(Channel length) 작을수록, W(dopant width) 클수록 Mobility ↑

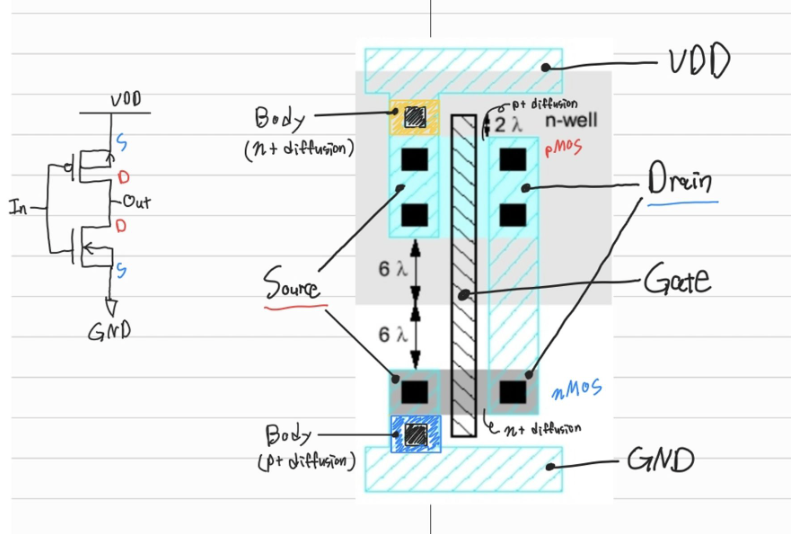

⦁ 수직, 수평 단면

왼쪽 그림은 nMOS와 pMOS의 mobility가 다른 점을 고려하지 않은 그림이고

오른쪽 그림이 mobility를 고려한 그림이다.

▶ pMOS의 p+ diffusion(w)를 2배로 → contact 2배

⦁ contact 큰 하나보다 작은 것 2개로 하는 것이 유리(저항 감)

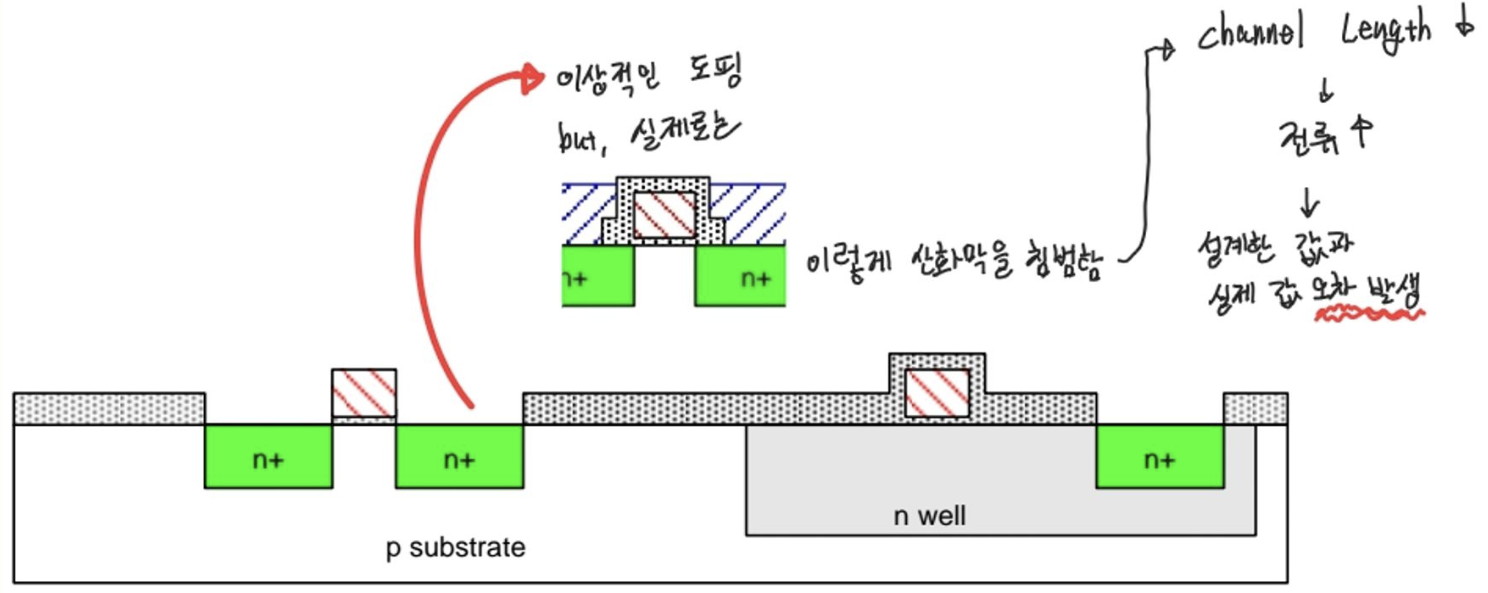

Diffusion Contact

이상적인 도핑과 실제 도핑에 차이 발생 → Channel Length 차이 발생 → 설계 전류와 실제 전류 차이 발생

Inverter Mask-set

Inverter CMOS Schematic과 Mask-set을 비교해보고 이해하자

그림에는 안나와 있지만

⦁ Input = Gate

⦁ Output = Drain

참고 문헌

CMOS VLSI Design: A Circuits and Systems Perspective [With Access Code] 제 4판

(Neil H. E. WesteDavid Money Harris, 한티에듀, 2021.02.05)

Made By Minseok KIM

'Full Custom IC > 이론' 카테고리의 다른 글

| [FullCustomIC] MOSFET 기본 이론(3)_Operation modes 등 (0) | 2024.03.09 |

|---|---|

| [FullCustomIC] MOSFET 기본 이론(2)_Stick Diagram 등 (0) | 2024.03.09 |

Let's Be Happy!

도움이 되었으면 좋겠어요 :)

![[FullCustomIC] MOSFET 기본 이론(3)_Operation modes 등](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fmx45C%2FbtsFDCeOmp6%2FArZiB3I7dhEI2sR26n1JD1%2Fimg.png)

![[FullCustomIC] MOSFET 기본 이론(2)_Stick Diagram 등](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcNiEhl%2FbtsFCBHbpL3%2FlUppciJaFhGPjmLdqcUPMK%2Fimg.png)