![[VerilogHDL] 조합 논리 회로 & 순차 논리 회로, Latch & FlipFlop](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FSF2r6%2FbtsHtOdeWqq%2Fj9KnstjOc4HKyuyYtH1lA0%2Fimg.png)

[VerilogHDL] 조합 논리 회로 & 순차 논리 회로, Latch & FlipFlopVerilogHDL/Study2024. 5. 19. 23:49

Table of Contents

1. 조합 논리 회로 & 순차 논리 회로

- 조합 논리 회로(Combinational Logical Circuit)

- 비동기 ← 클럭에 영향을 받지 않음 ⇒ 입력이 들어가면 출력이 바로 나옴

- MUX, Decoder, DigitSplitter, Gates(AND, OR, …), ALU

- 순차 논리 회로(Sequential Logic Circuit)

- 동기 ← 클럭에 영향을 받음 ⇒ 클럭을 기준으로 동작 시점 결정

- Clock Diver, Counter, Flip-Flop(Edge Trigger), Latch(Level Trigger), Register

클럭을 쓰는 이유?

- 동기화 : 동시에 무엇인가 동작, 동작을 시키기 위한 기준점

- 데이터 무결성 향상

- 시스템 안정성 → 시스템이 정확한 시간, 원하는 타이밍에 동작

- 병렬 처리 → 여러 작업이 동시에 혹은 병렬적으로 실행 될 수 있음

- 파워 관리

2. Latch & Flip-Flop

- Memory 기능

기본 구조

⇒ NOT Gate 2개를 붙인 형태(SRAM 구조(오른쪽 그림))

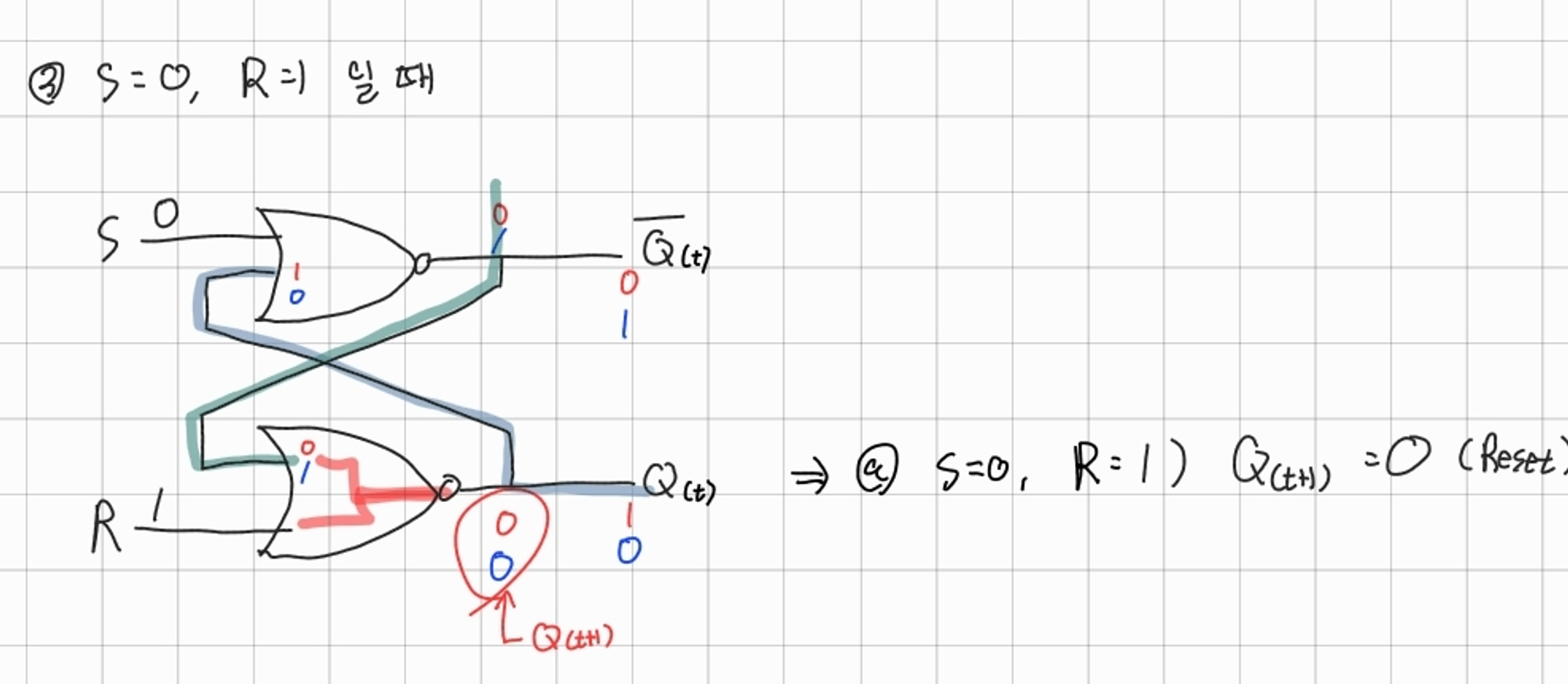

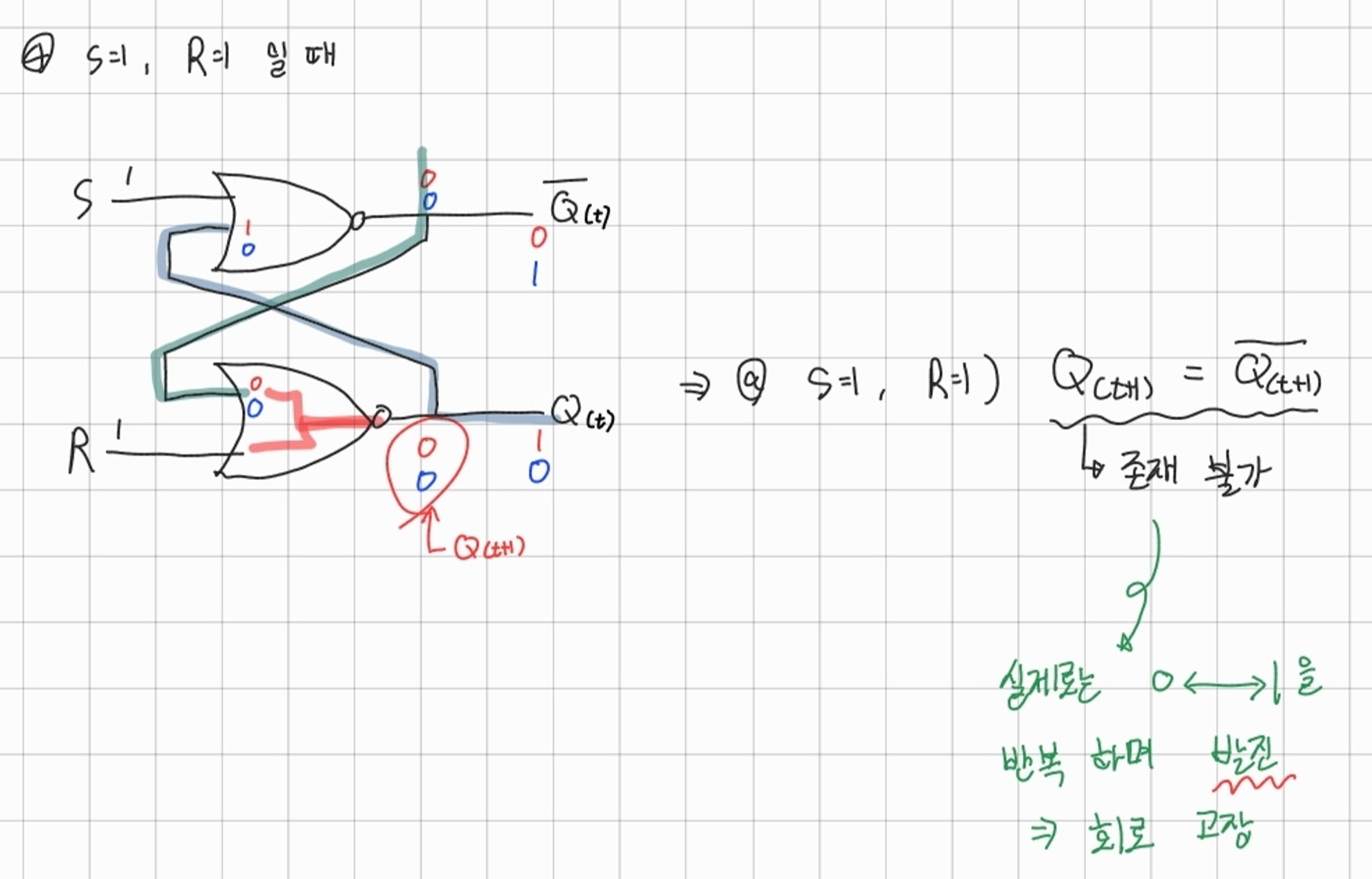

2-1. SR Latch

| S | R | Q(t+1) |

| 0 | 0 | Q(t) |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | X |

⇒ S = 0, R = 0일 때 이전 값을 유지한다 → 메모리 기능

SR Latch 동작 원리

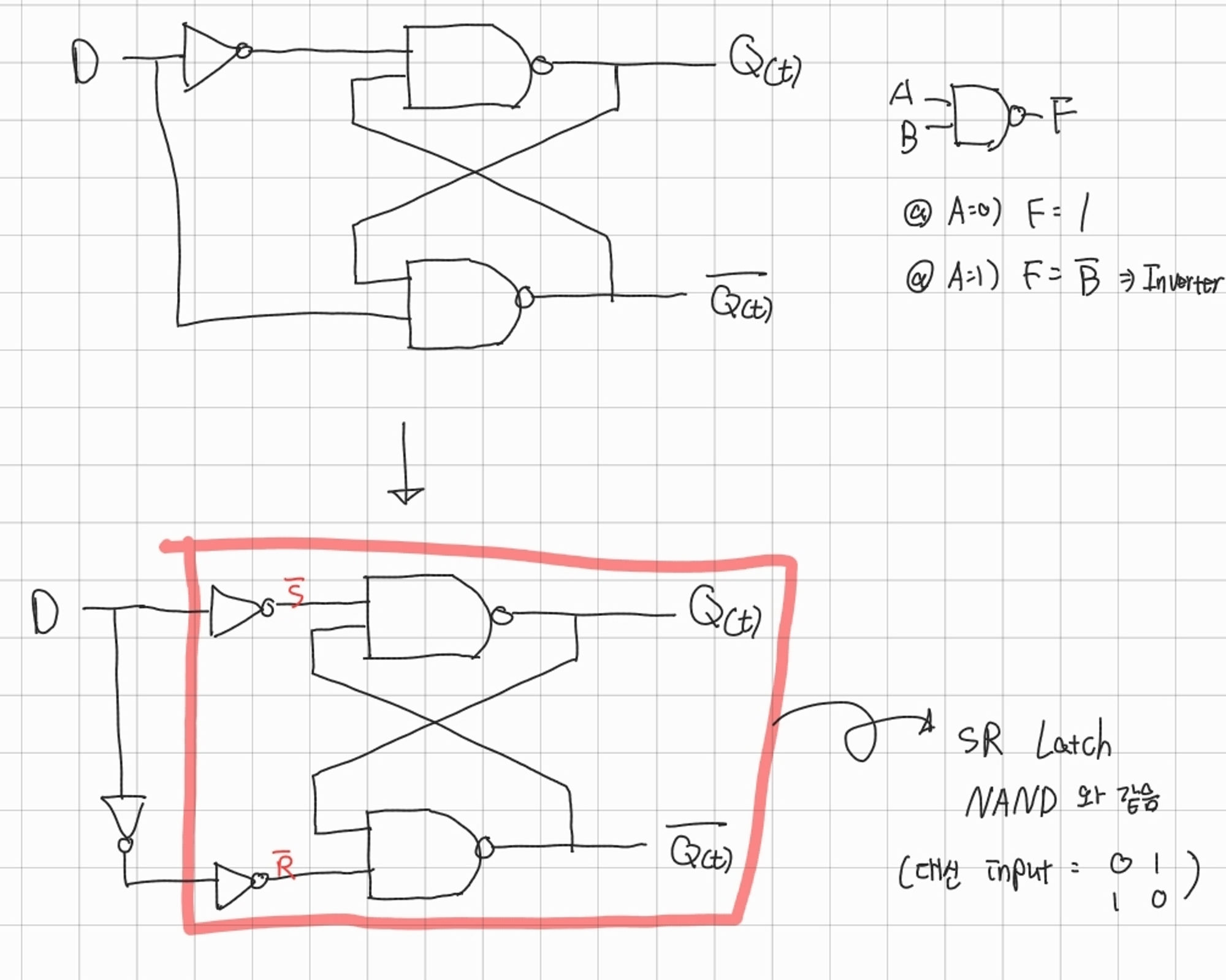

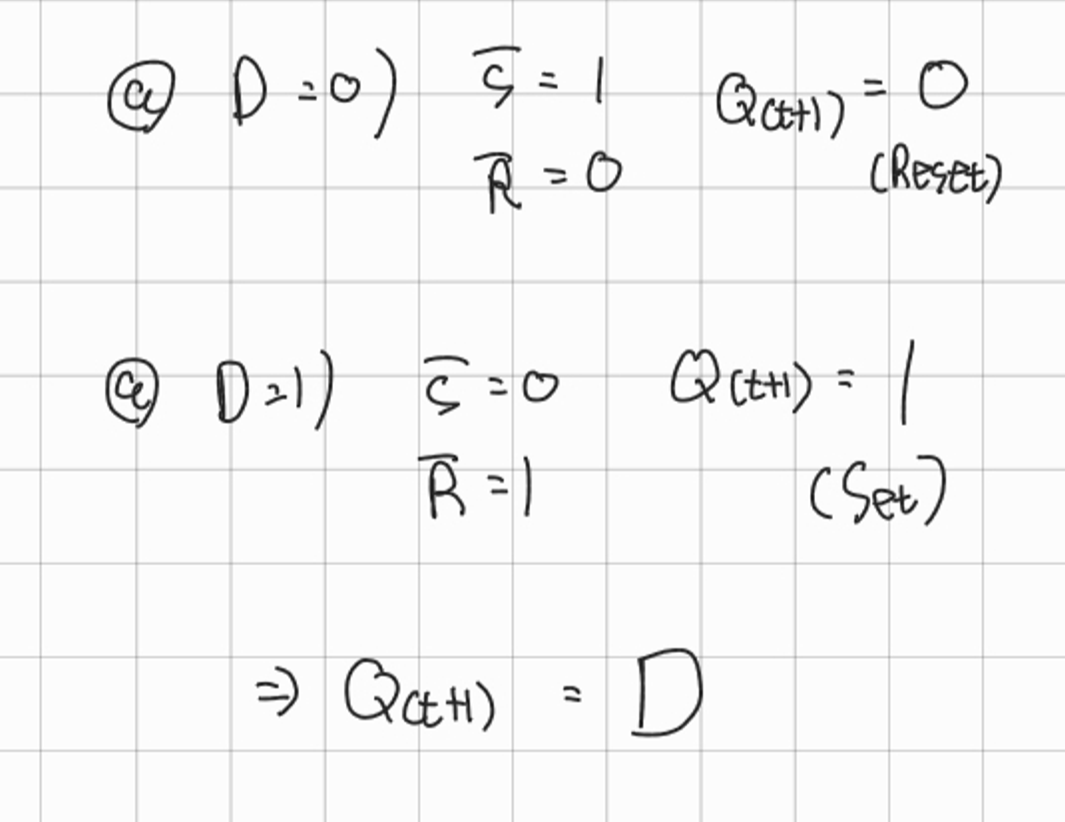

2-2. D Latch

| D | Q(t+1) |

| 0 | 0 |

| 1 | 1 |

Gate/Pulse D Latch

- D Latch에 클럭 신호 입력 추가

- CLK : 1) Update, CLK : 0) Hold

⇒ 클럭의 레벨(High/Low)에 따라 출력의 상태가 변경됨 → Level Trigger

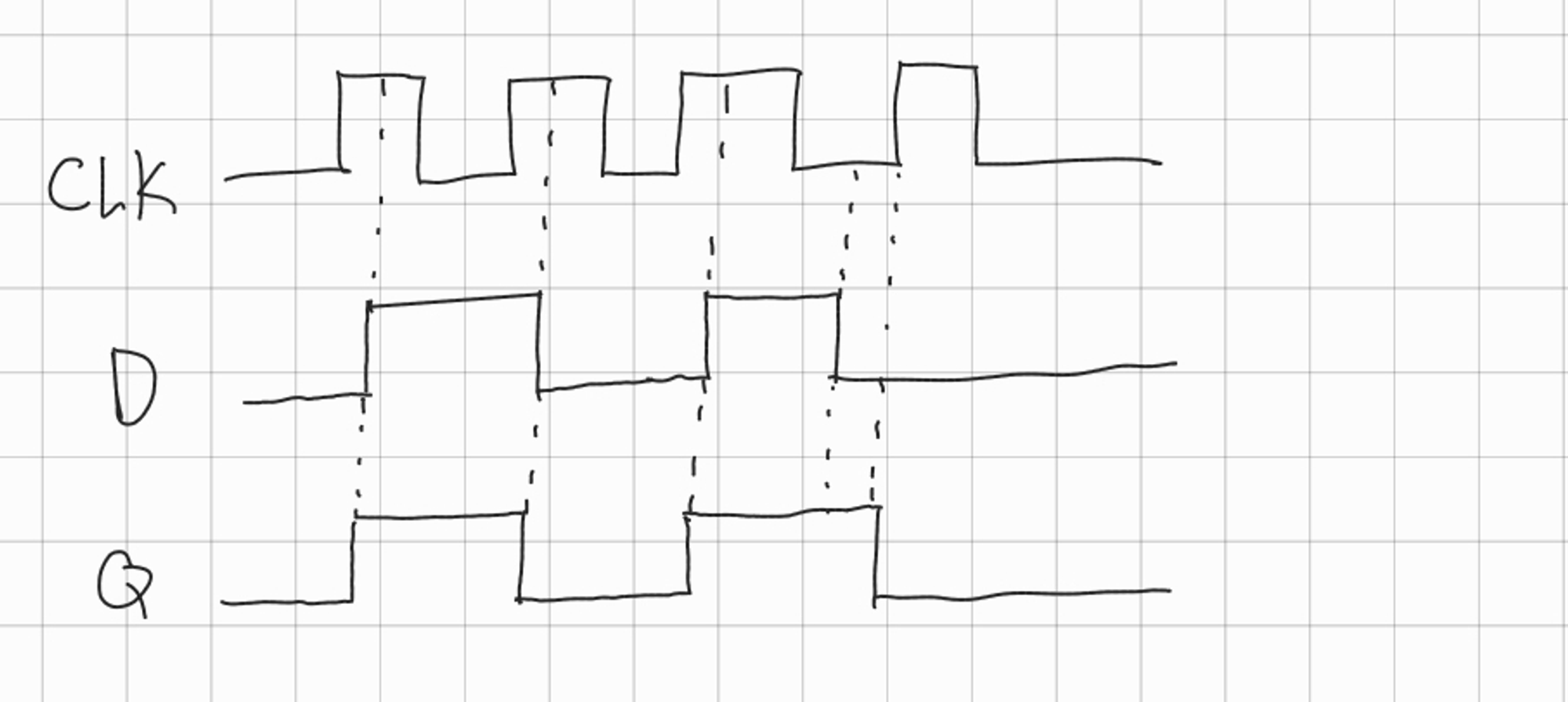

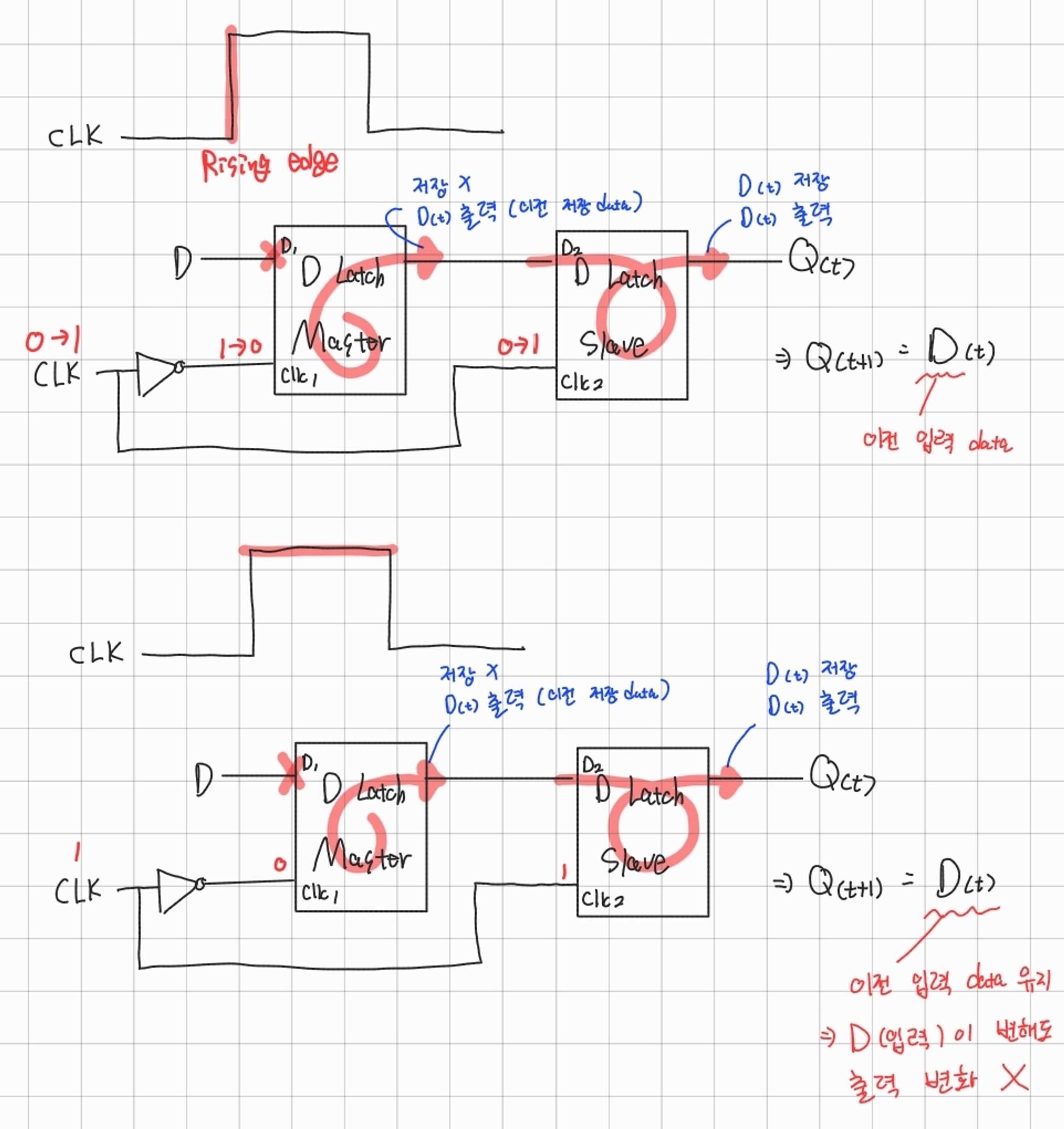

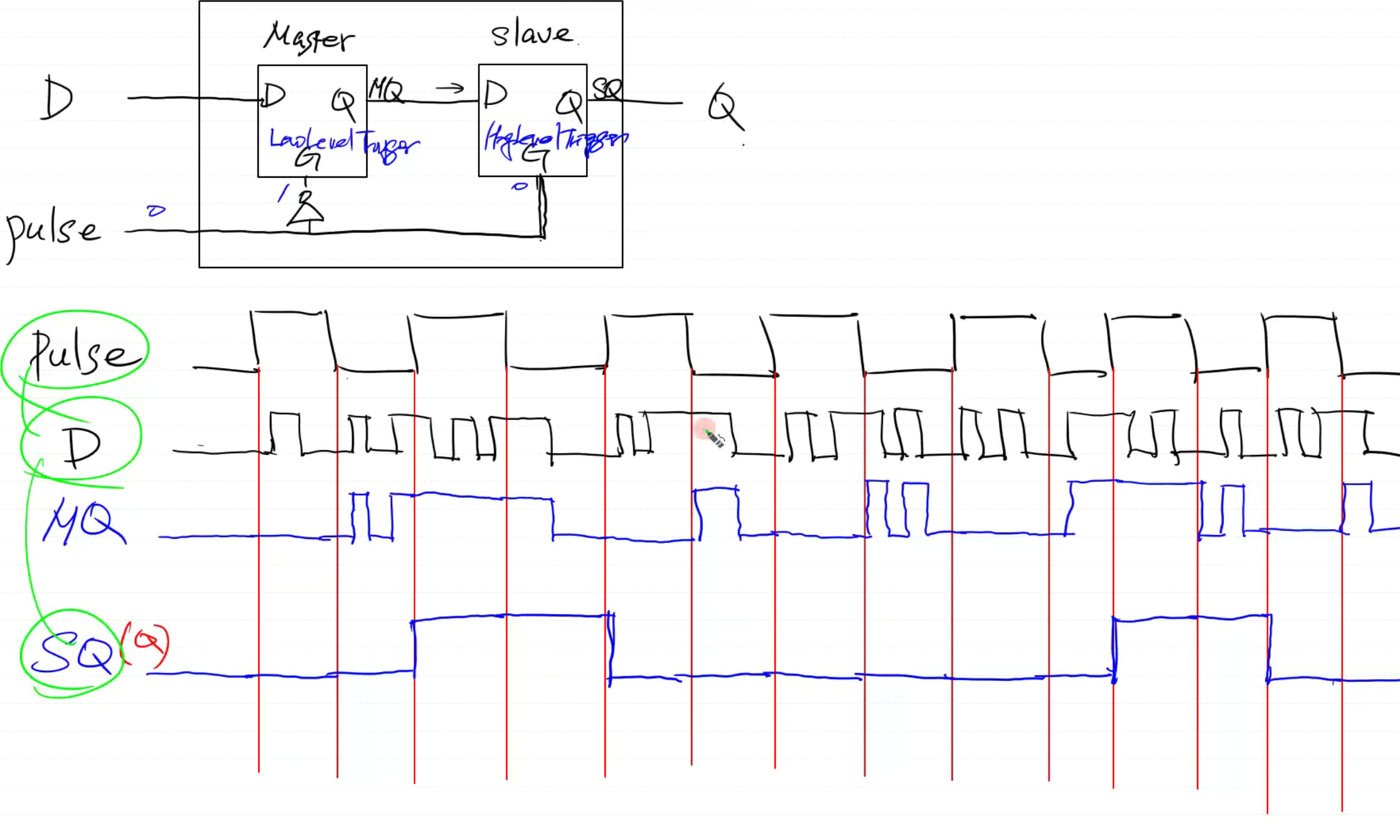

2-3. D Flip-Flop

- 2개의 D Latch를 연결(Master & Slave)

⇒출력 Q는 CLK가 Rising edge 일 때 이전 data로 Update & 그 외에는 Hold

→ Edge Trigger

- NOT Gate가 Master Latch에 있으면 Rising edge Trigger, Slave Latch에 있으면 Falling edge Trigger

Level Trigger & Edge Trigger

⦁ D Latch

∘ Level Trigger

∘ CLK의 High 신호에서 동작

∘ CLK High 신호일때 그 안에 입력 값이 바뀔 때 마다 출력값도 계속 바뀜

⦁ D Flip-Flop

∘ Edge Trigger

∘ CLK의 Edge에서 동작

∘ CLK이 Edge일 때에만 출력 값이 update

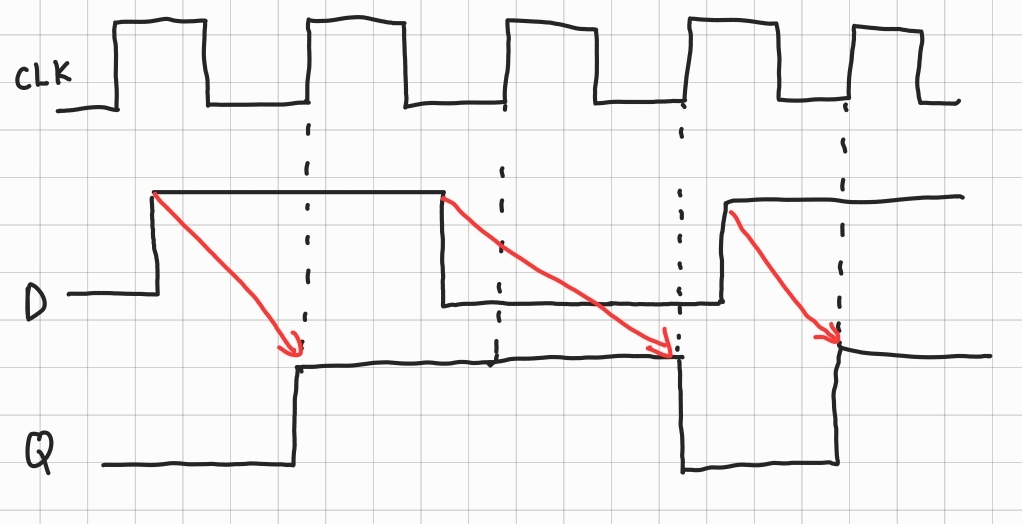

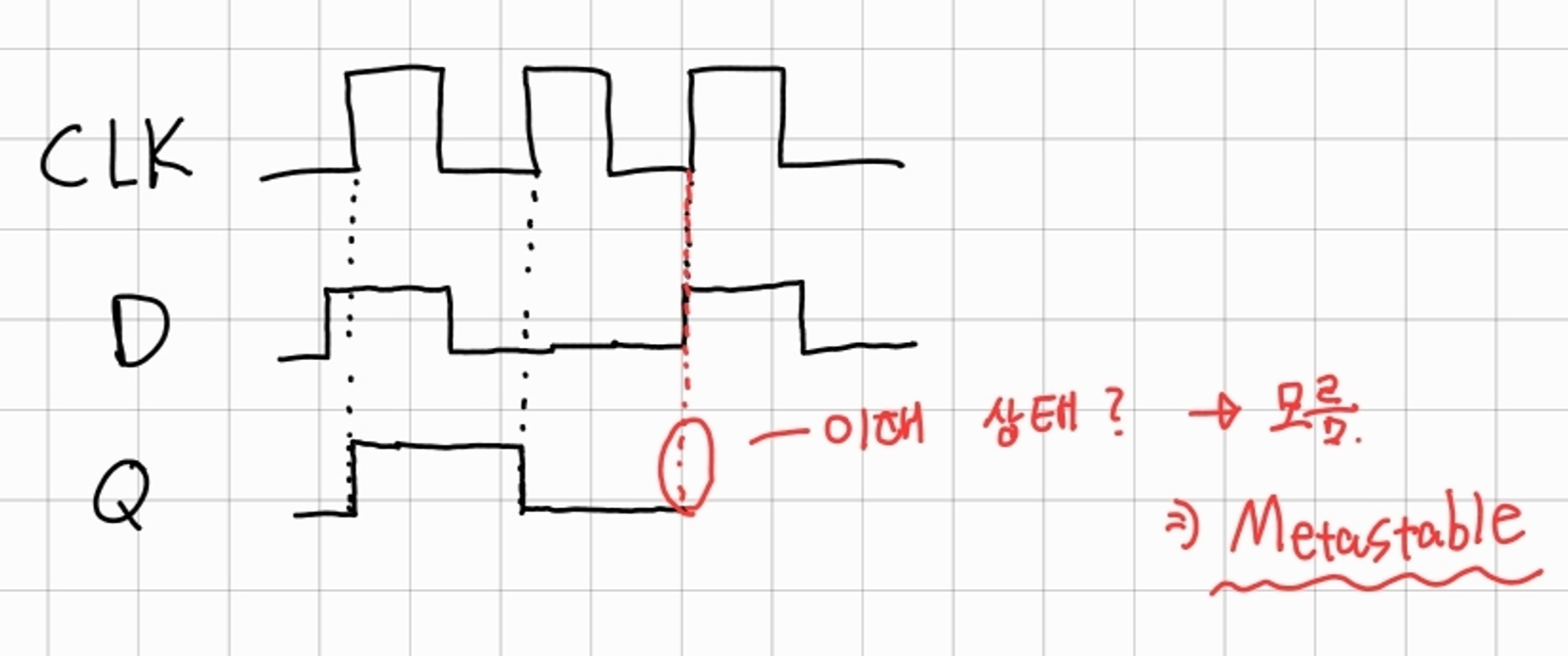

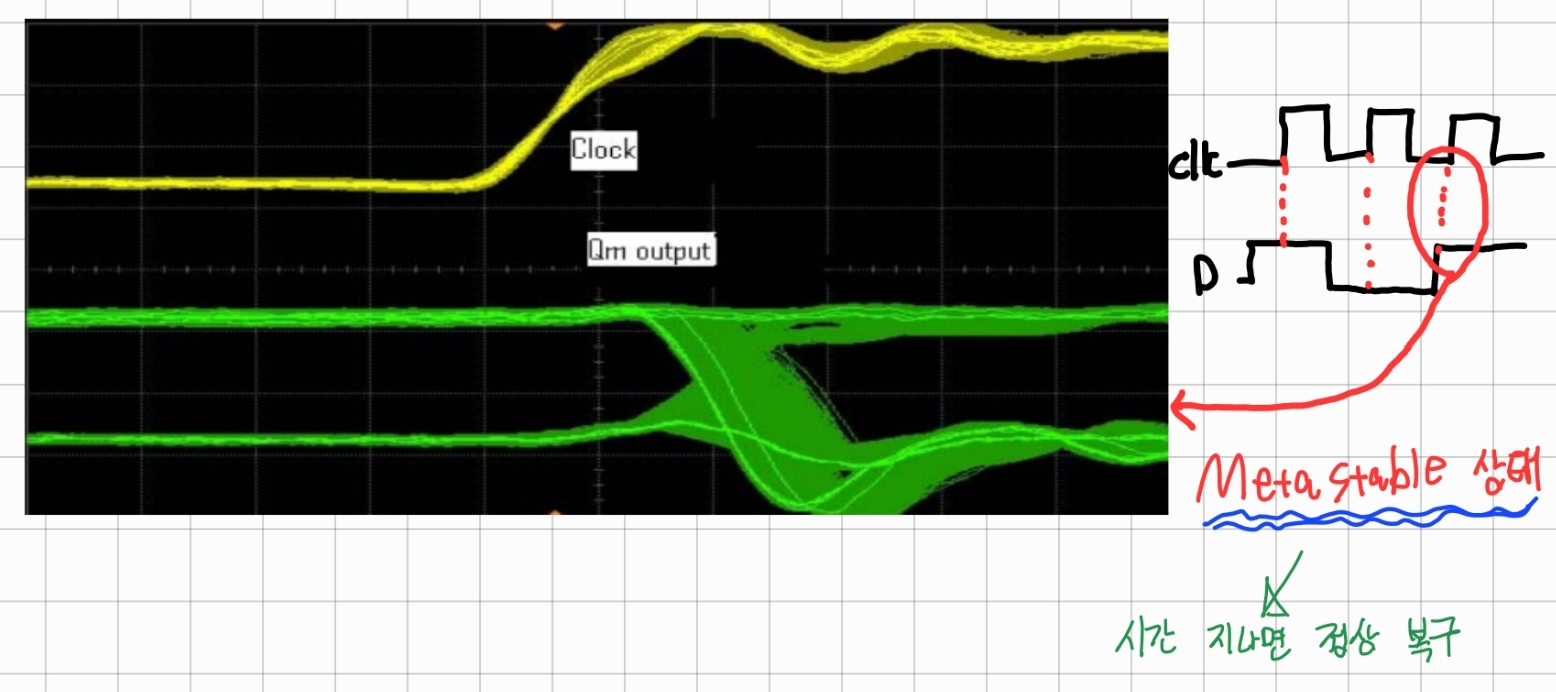

2-4. Setup time & Hold time

위 (1) 그림에서 보면 Setup time 혹은 Hold time이 너무 짧을 경우 원하는 상태(High)가 업데이트 되지 않음

⇒ Metastable 상태

Setup time

⦁ 클럭이 Edge 전 입력 D 유지 시간

→ 클럭 Edge 이전에 어느정도 입력을 유지해야함

Hold time

⦁ 클럭이 Edge 후 D 유지 시간

→ 클럭 Edge 이후에 어느정도 입력을 유지해야함

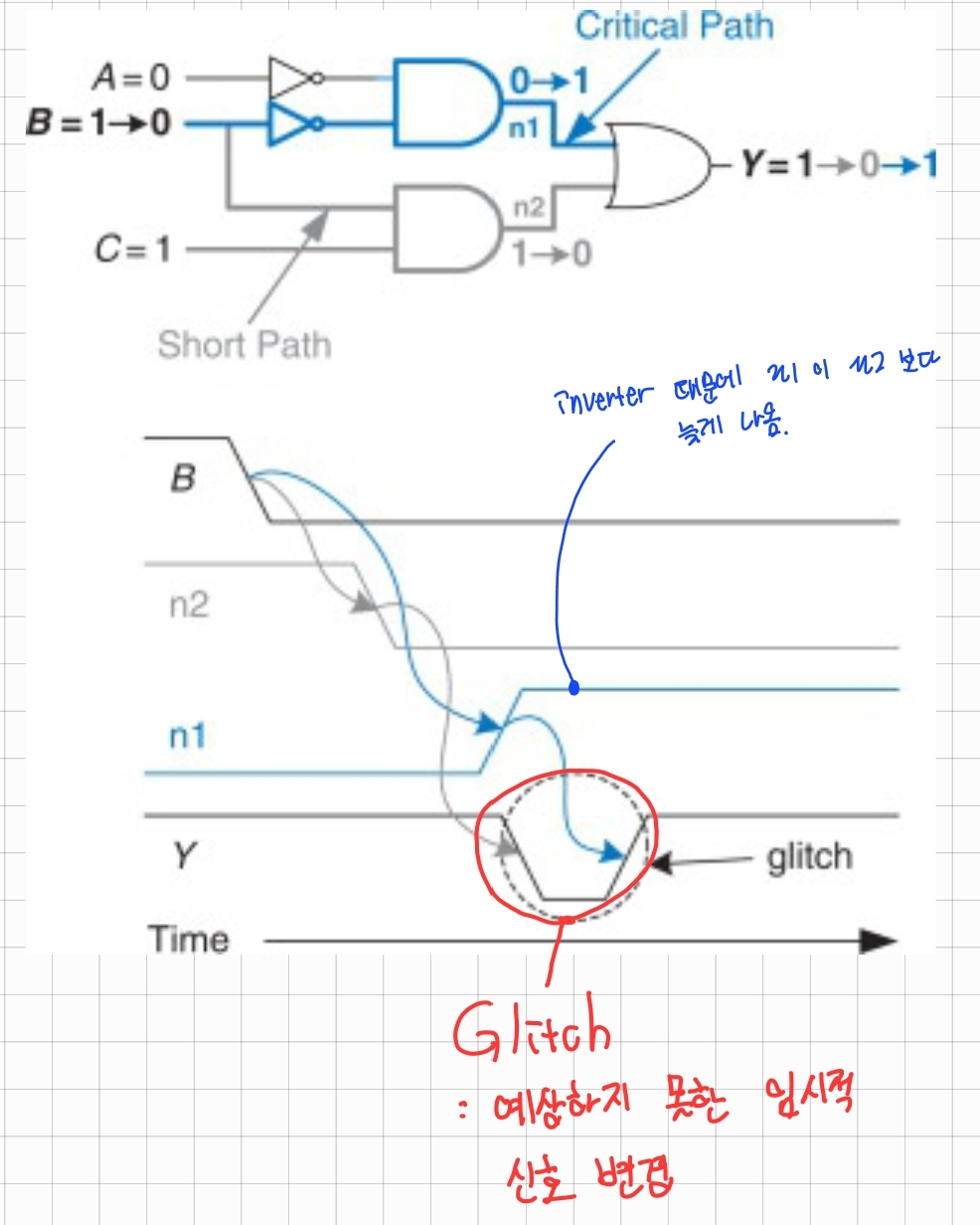

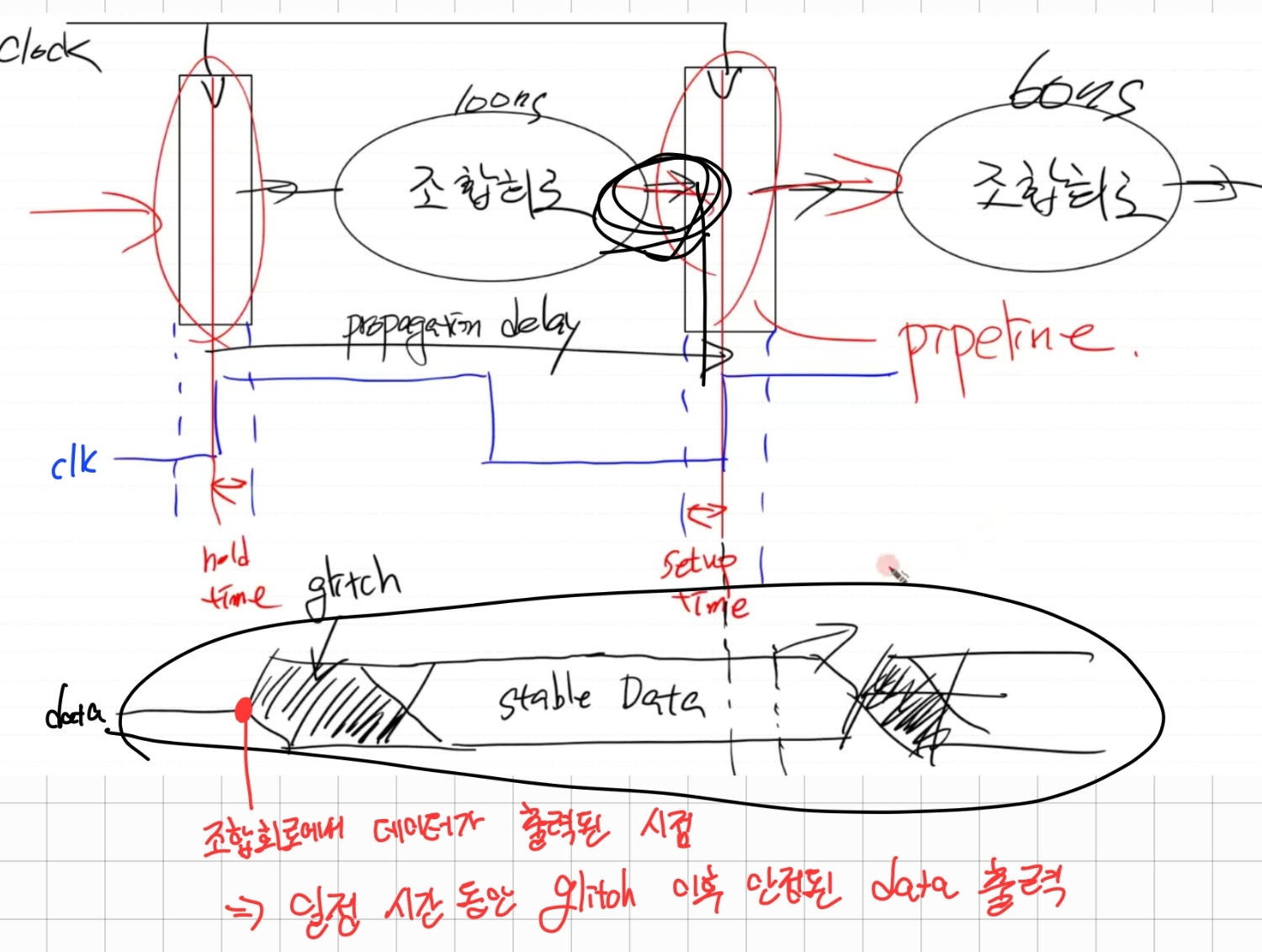

3. 순차 회로를 쓰는 이유

- Glitch 상태를 줄이기 위해..

조합 회로만 사용하면 위와 같이 Glitch가 발생 할 수 있음

⇒ 순차 회로를 통해 클럭으로 동기화를 한다.

⦁ 클럭 주기는 Setup time + Hold time + Propagation delay (ts + th + tp) 이상으로 설정

→ 클럭의 주기가 그 이하가 된다면 데이터가 처리되기 전 다음 클럭으로 인해 출력에 오류가 생길 수 있음.

- Propagation delay

- 입력이 변경된 후 출력이 해당 변경을 반영하는 데 걸리는 시간

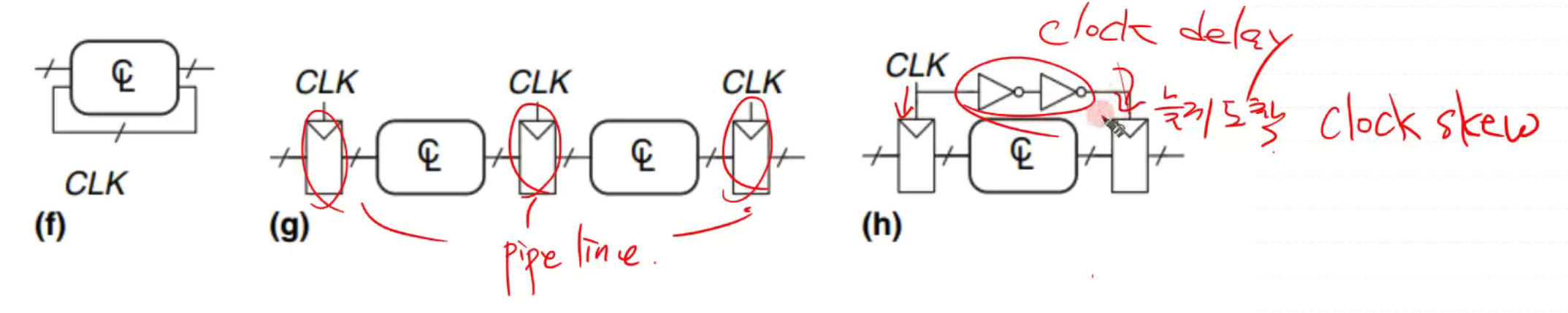

- Pipe line

- 순차 회로(레지스터 등), 조합 회로, 순차 회로, 조합 회로 순으로 연결하는 것

- skew

- 클록 신호가 시스템의 여러 부분에 도달할 때 발생하는 시간 차이

Made By Minseok KIM

'VerilogHDL > Study' 카테고리의 다른 글

| [VerilogHDL] UpCounter, 디버깅, UART Tx (0) | 2024.05.20 |

|---|---|

| [VerilogHDL] FSM 코딩(Moore, Mealy) - 버튼, UpCounter (0) | 2024.05.19 |

| [VerilogHDL] C&Verilog차이, SystemVerilog 기본, 8bit Adder FND, 만진 카운터 (0) | 2024.05.16 |

| [VerilogHDL] System Verilog, 4bit Adder FND 출력 (0) | 2024.05.16 |

| [VerilogHDL] HalfAdder, FullAdder, 4bit Adder (0) | 2024.05.09 |

@민바Minba :: Minba's blog

Let's Be Happy!

도움이 되었으면 좋겠어요 :)

![[VerilogHDL] UpCounter, 디버깅, UART Tx](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FrNZdr%2FbtsHt4GKhkZ%2FSqEK0mIH4LejNPLqR0OIQK%2Fimg.png)

![[VerilogHDL] FSM 코딩(Moore, Mealy) - 버튼, UpCounter](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fbetzc8%2FbtsHvuRSMN0%2FQWuDHrBhsfysBOnJnirWy1%2Fimg.png)

![[VerilogHDL] C&Verilog차이, SystemVerilog 기본, 8bit Adder FND, 만진 카운터](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FHWO9v%2FbtsHqbzgbYD%2FUAoHdNYYi9zPTYOsETtu81%2Fimg.png)

![[VerilogHDL] System Verilog, 4bit Adder FND 출력](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbpRigX%2FbtsHp32iq76%2FekHf18H6oq2HZElY9OjyTk%2Fimg.png)