![[FullCustomIC] Cadence Virtuoso_4bit Adder, Subtractor](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2F5wOVW%2FbtsGNtUHsfG%2FrAE7kW1Bf8vynwYpWDvHD1%2Fimg.png)

1. 4bit Adder

Half Adder 1개, Full Adder 3개가 직렬로 이어져 있는 형태

→ 각각의 Adder가 각 자리수에 대한 연산 시행

- test setup

| VDD | VSS | VINH | |

| source type | DC 1V | DC 0V | Pulse |

| Voltage range | x | x | 0 ~ 1V |

| Period | x | x | 20n |

| Delay time | x | x | 0s |

| Rise time | x | x | 1ps |

| Fall time | x | x | 1ps |

| Pulse width | x | x | 10n |

| Simulation time | 30ns | ||

0111 (VING, VINE, VINC, VINA)

x100 (VINH, VINF, VIND, VINB)

→ VINH의 값만 0, 1로 바꾸어 연산 결과 확인

VINH = 0)

0111 + 0100 (7+4) = 1011 (=11)

VINH = 1)

0111 + 1100 (7+12) = 1 0011 (=19) ← Carry 발생

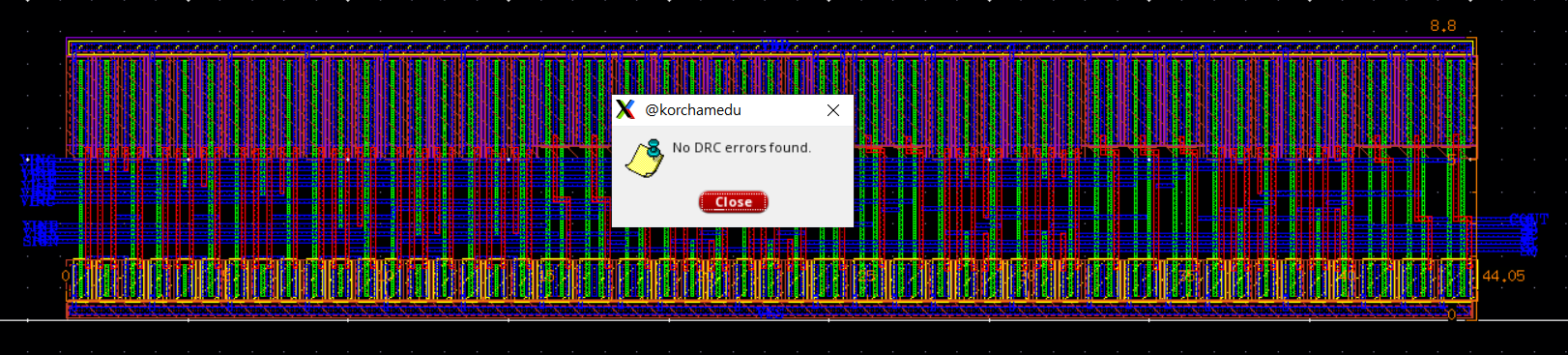

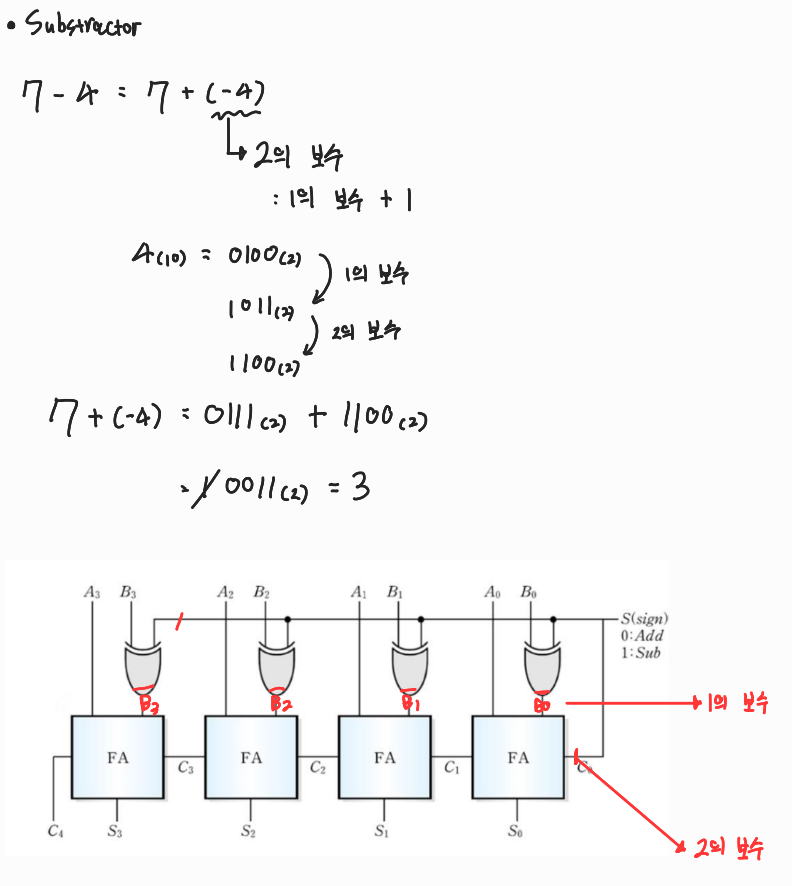

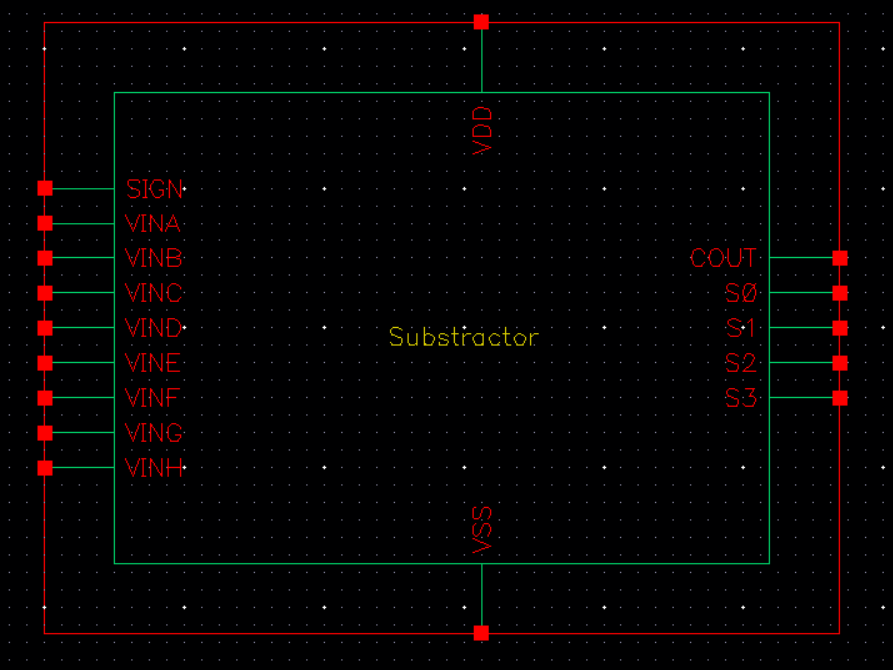

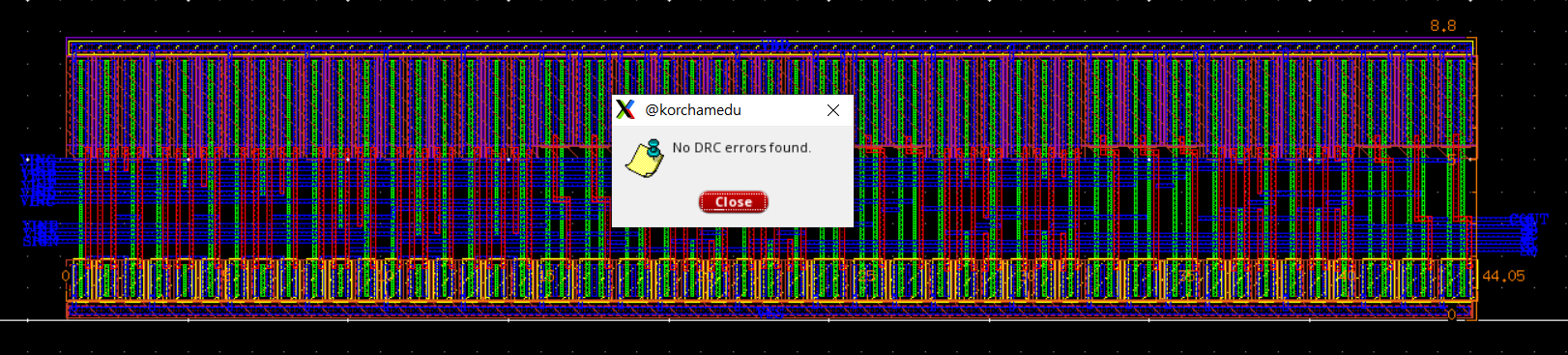

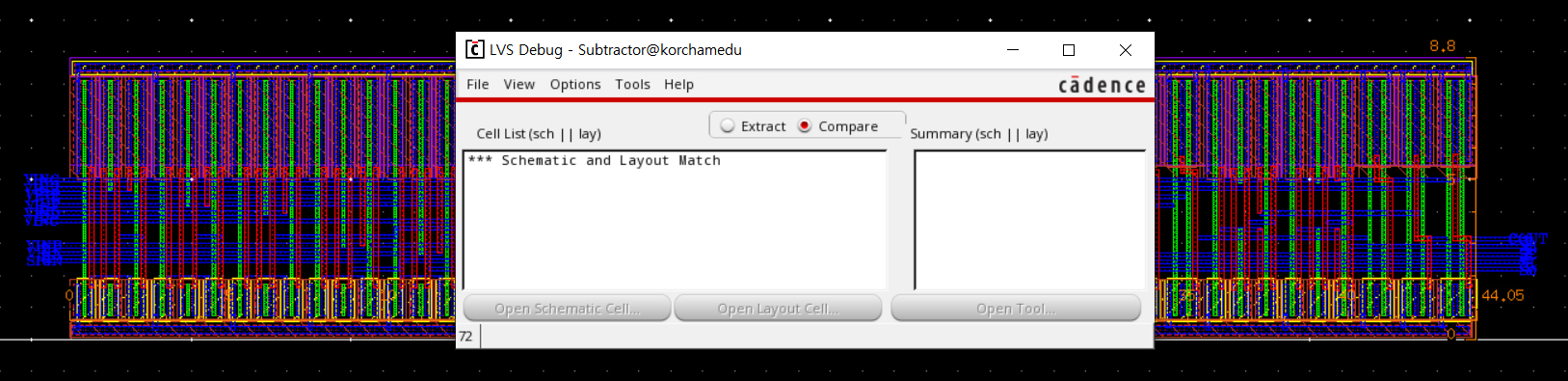

2. Subtractor

CTRL bit = 0) 덧셈 연산

CTRL bit = 1) 뺄셈 연산

뺄셈 연산

: 2의 보수 취한 뒤 덧셈 연산

- XOR Gate로 1의 보수를 취하고

- 첫번째 Full Adder CIN으로 1을 입력하여 +1 함으로써 2의 보수 완성

- test setting

| VDD | VSS | VINB | SING | |

| source type | DC 1V | DC 0V | Pulse | Pulse |

| Voltage range | x | x | 0 ~ 1V | 0 ~ 1V |

| Period | x | x | 20n | 40n |

| Delay time | x | x | 0s | 0s |

| Rise time | x | x | 1ps | 1ps |

| Fall time | x | x | 1ps | 1ps |

| Pulse width | x | x | 10n | 20n |

| Simulation time | 50n | |||

1110 (VING, VINE, VINC, VINA)

x001 (VINH, VINF, VIND, VINB)

→ VINH의 값만 0, 1로 바꾸어 연산 결과 확인

SIGN = 0)

VINH = 0)

1110 + 0001 (14+1) = 0 1111 (15)

VINH = 1)

1110 + 1001 (14+9) = 1 0111 (23)

SIGN = 1)

VINH = 0)

1110 - 0001 (14-1) = 0 1101 (13)

VINH = 1)

1110 - 1001 (14-9) = 0 0101 (5)

→ 뺄셈 연산의 Carry는 부호를 의미한다.

Made By Minseok KIM

'Full Custom IC > Study' 카테고리의 다른 글

Let's Be Happy!

도움이 되었으면 좋겠어요 :)

![[FullCustomIC] Cadence Virtuoso_XOR Gate, Adder](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fdb5VmG%2FbtsGMR9ylC2%2FBJPs4F0KbIkx4mAmfDMvZk%2Fimg.png)

![[FullCustomIC] Cadence Virtuoso_4x1 MUX(Logic, Switch), 8x1 MUX(Logic, Switch), 16x1 MUX(Logic, Switch)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FdVwZjp%2FbtsGOJ3evbp%2FPgYCH6Fcc68e512rCohIx1%2Fimg.png)

![[FullCustomIC] Cadence Virtuoso_Switch, 2x1 MUX(Switch)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbYl2vA%2FbtsF1IZozT4%2Fapfqi8DFiPOGfE0DlKNm6k%2Fimg.jpg)

![[FullCustomIC] Cadence Virtuoso_4NAND, 4NOR, 2x1 MUX(Logic)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fca8sxr%2FbtsF1DxdVDb%2FauAx2QwgjlMpHNKM7EKmH1%2Fimg.png)