![[FullCustomIC] Cadence Virtuoso_Switch, 2x1 MUX(Switch)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FbYl2vA%2FbtsF1IZozT4%2Fapfqi8DFiPOGfE0DlKNm6k%2Fimg.jpg)

Swtich Level Design

⦁ Logic Level Design은 AND, OR 등 논리 게이트를 이용하여 설계하는 방법

⦁ Switch Level Design은 스위치 상태를 고려하여 설계하는 방법(Switch 이용)

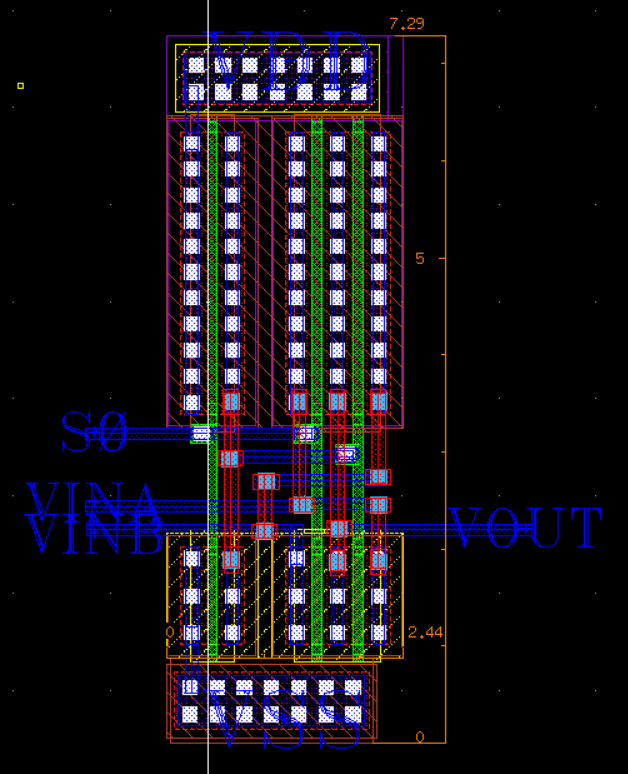

위 Switch의 특이한 점은 Source와 Body가 연결되어 있지 않다.

(pMOS Gate와 nMOS Gate가 둘 다 S0여서 정상동작하는 스위치는 아니지만 여기서는 Switch Level Design을 이해하기 위해 최대한 단순하게 표현)

각 Gate로 S0라는 control 신호가 입력되고 VIN이 pMOS Source와 nMOS Drain으로 입력

즉, 입력 단자가 2개(VDD, VSS 제외)

→ VIN으로 특정 신호를 흘려보내면 S0로 제어하여 VOUT으로 신호 출력 가능

(Source와 Body를 묶어버리면 0(VSS) 또는 1(VDD)만 출력하고 신호를 출력할 수는 없다. (입력 단자 VIN 1개))

→ pMOS Width는 NOT Gate Simulation 결과를 통해 알 수 있다.(똑같이 pMOS 1개, nMOS 1개 사용) = 2.91u

→ Schematic에서 Source와 Body가 연결되어 있지 않아 Layout에서도 VDD, VSS와 연결이 되어 있지 않는 것을 볼 수 있다.

2x1 MUX(Switch)

[FullCustomIC] Cadence Virtuoso_4NAND, 4NOR, 2x1 MUX(Logic)

1. 4NAND Gate ⦁ 4NAND Truth Table VINA VINB VINC VIND VOUT 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 - pMOS w = 2.14u, nMOS w = 1u - pMO

minba-dev.tistory.com

이전에 설계하였던 2x1 MUX는 2NAND Gate 3개를 연결한 Logic Level Design이고

이번에는 Switch를 이용하여 Switch Level 2x1 MUX Design한다.

⦁ test set

| VDD | VSS | VINA | VINB | S0 | |

| source type | DC 1V | DC 0V | DC 1V | Pulse | Pulse |

| Voltage range | x | x | x | 0 ~ 1V | 0 ~ 1V |

| Period | x | x | x | 50ns | 400ns |

| Delay time | x | x | x | 0s | 0s |

| Rise time | x | x | x | 1ps | 1ps |

| Fall time | x | x | x | 1ps | 1ps |

| Pulse width | x | x | x | 25ns | 200ns |

| Simulation time | 1.2us | ||||

→ Simulation 결과가 이전 Logic Level Design과 같은 것을 볼 수 있다.

비교

Switch Level Design이 Logic Level Design보다 훨씬 작은 것을 확인할 수 있다.(TR개수 14개 → 6개)

Made By Minseok KIM

'Full Custom IC > Study' 카테고리의 다른 글

Let's Be Happy!

도움이 되었으면 좋겠어요 :)

![[FullCustomIC] Cadence Virtuoso_XOR Gate, Adder](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fdb5VmG%2FbtsGMR9ylC2%2FBJPs4F0KbIkx4mAmfDMvZk%2Fimg.png)

![[FullCustomIC] Cadence Virtuoso_4x1 MUX(Logic, Switch), 8x1 MUX(Logic, Switch), 16x1 MUX(Logic, Switch)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FdVwZjp%2FbtsGOJ3evbp%2FPgYCH6Fcc68e512rCohIx1%2Fimg.png)

![[FullCustomIC] Cadence Virtuoso_4NAND, 4NOR, 2x1 MUX(Logic)](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2Fca8sxr%2FbtsF1DxdVDb%2FauAx2QwgjlMpHNKM7EKmH1%2Fimg.png)

![[FullCustomIC] Cadence Virtuoso_2NAND, 2NOR, 3NAND, 3NOR Gate Layout](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FcxW540%2FbtsF10MgiWT%2FmV3Irz0o5ojSwxgFbqHf01%2Fimg.png)